Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

H2068 is a high-performance dual-core processor chip with embedded 32-bit C9500 core of PowerPC architecture, featuring Gigabit Ethernet interface, PCIE 1.0 interface, RapidIO interface, DDR controller, PCI controller, and commonly used SPI, UART, I2C interfaces. It includes high-performance data path interface logic, networks, and peripheral buses required for network interconnection, telecommunications/data communication, and wireless infrastructure applications.

It can be used for integrated control, data path, and application layer processing in routers, switches, base station controllers, and general embedded computing. Compared with multiple discrete devices, its high integration offers significant performance advantages and greatly simplifies the design of the circuit board.

The benchmark chip is NXP MPC8568.

H2068 has achieved localized and domestic production in terms of design, manufacturing, packaging and testing.

Block Diagram

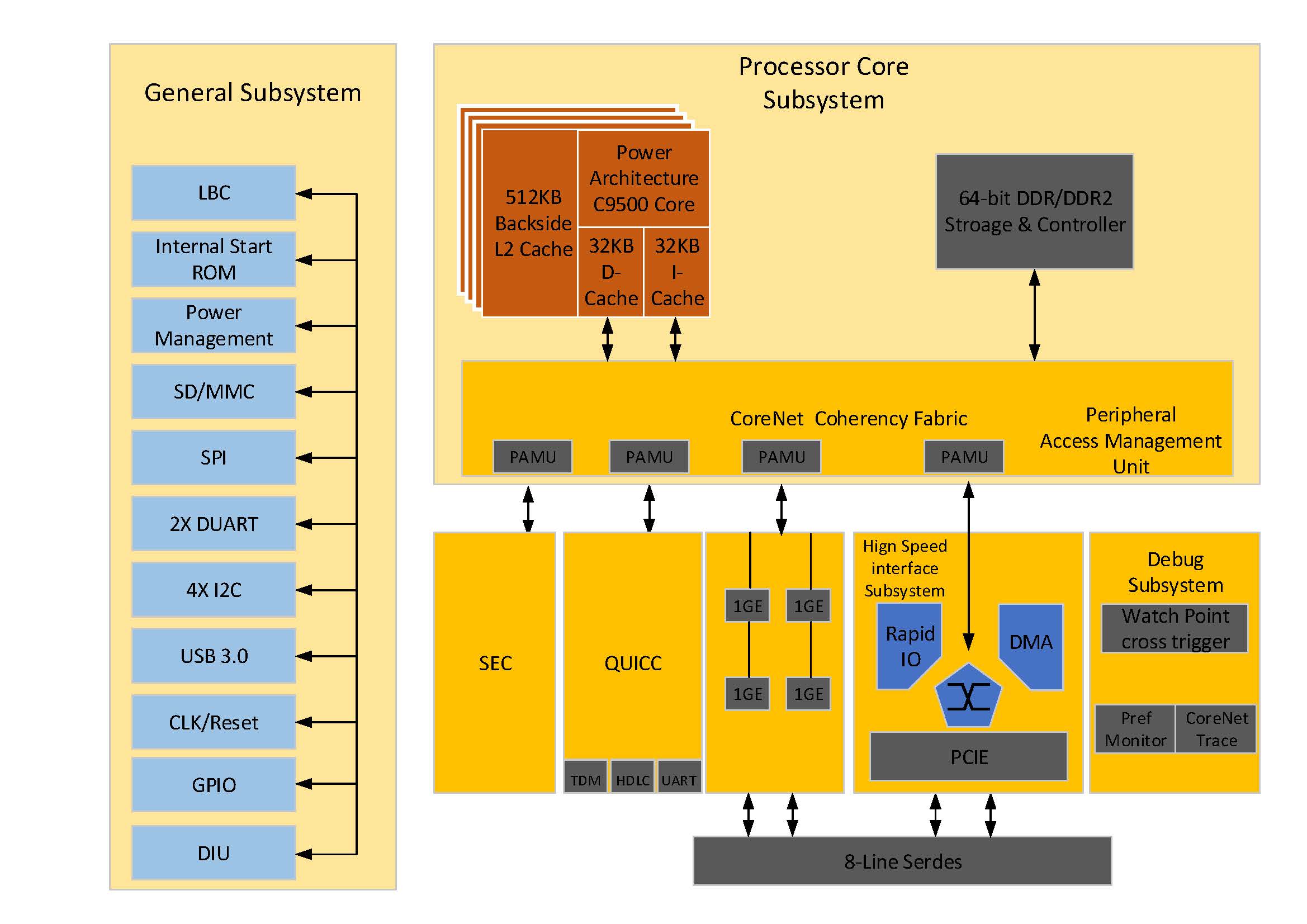

The H2068 chip takes C9500 as the main core while taking an algorithm security engine as a coprocessor for implementing various cryptographic algorithms.In addition, it is equipped with necessary RAM resources and corresponding security protection mechanisms, supplemented by various peripheral interfaces such as USB, RapidIO, PCIE, etc. The composition is shown in the below figure :

★ C9500 Core: Compatible with NXP PowerPC e500MC core

★ Memory Resources: 512KB SRAM

★ DDR/DDR2 Controller: Supports DDR1/DDR2 type memory

★ CoreNet Coherence Fabric (CCF): Supports Power architecture coherence operations; Supports debugging

★ eLBC Bus Controller: Contains 8 memory banks

★ SEC Engine: Supports automatic hardware scheduling for algorithms; Supports international standard cryptographic algorithms such as AES, RSA, ECC; Supports national cryptographic algorithms such as SM2, SM3, SM4

★ PCI/PCIX Interface: Supports standard PCI/PCIX interface

★ PCIE 1.0 Interface: 1 channel

★ Serial RapidIO 1.2: 1 channel

★ Gigabit Ethernet Controller: Integrated with 4 GMII interfaces

★ SPI Interface: 1 channel

★ UART Interface: 2 channels

★ I2C Interface: 4 channels

★ GPIO: 32 channels

★ Chip Debugging: Supports JTAG debugging interface for software debugging

★ QUICC Engine: Features a 32-bit RISC processor; Supports TDM, HDLC, and UART

★ Packaging: BGA783

★ Temperature Range: Operating temperature -55℃~125℃; Storage temperature -65℃~150℃