Chip Services

Chip Services

Products

Products

- Automotive and Industrial control

- Information Security

- Edge Computing& Network Communication

Products

Resources

Resources

Language

Language

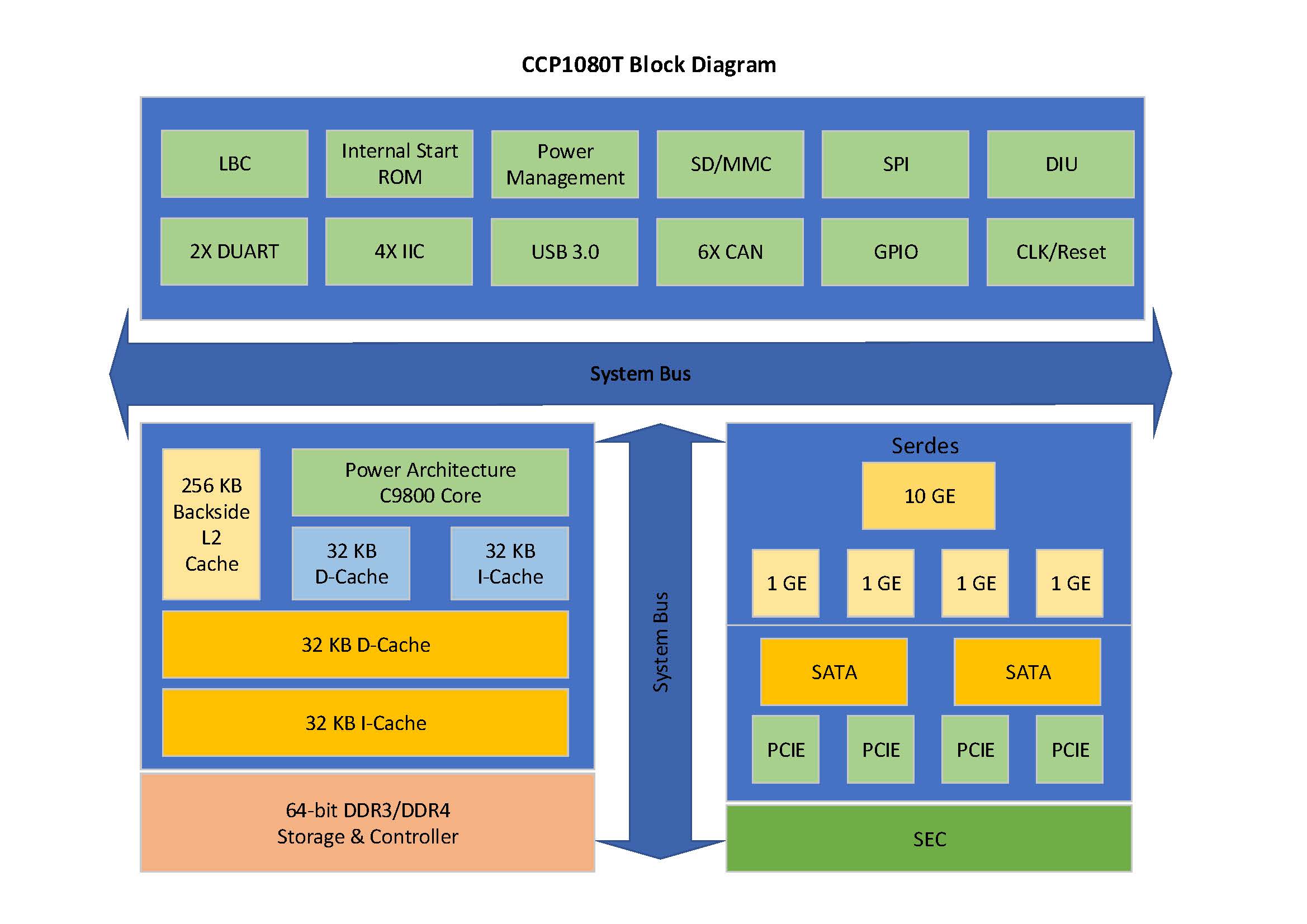

The CCP1080T chip is a new generation of high-performance and high-security edge computing chip based on C*Core’s 64-bit PowerPC architecture CPU core. C9800 is high-performance dual-core with operating frequency up to 1.8GHz under normal conditions and a Dhrystone performance of 3.1DMIPS/Mhz.

CCP1080T integrates the high-performance security computing processing unit SPU. It supports secure boot and meets the relevant standards for national cryptographic security processors.It can be applied in areas such as servers, security gateways, cryptographic machines, routers, firewalls, industrial control computers, PLCs, intelligent roadside equipment, and small network base stations as a security coprocessor chip or a main controller chip with security functions.

? Compatible with NXP 64-bit e5500 core which supports the PowerPC V2.06 instruction set . The processor core has three privilege levels according to the instruction set: user, supervisor, hypervisor

? Dual-core architecture, with each core enjoying exclusive access to 32KB L1 ICache, 32KB L1 DCache, and 256KB L2 Cache

? Supporting a maximum physical memory space of 64 GB , with big/little-endian access per page

? Supporting external tamper detection for bootloader

? Security fuse module

? Security monitoring module

? Internal and external code signature

? Data secure storage:

- Unique Blob mechanism for secure storage of sensitive data in off-chip Flash

- Mechanism for destroying sensitive data within the chip in the event of a security violation

- Supporting a rich set of physical attack defense mechanisms

? Built-in multi-core public key, symmetric, and hash algorithm units, random number generator

- True random number engine with 4 independent clocks

- Symmetric algorithm acceleration engine: SM4/AES/DES/3DES

- Digest algorithm acceleration engine:

SHA0/SHA1/SHA224/SHA256/

SHA384/SHA512/SM3/MD5/HMAC

- Public key algorithm acceleration engine (PKHA):

SM2/SM9/RSA(4096bit)/DH(4096bit)/ ECC(1024bit)

? Supporting 2 chip selects, DDR4 devices ranging from 64Mbit to 8Gbit

? Programmable settings to meet all SDRAM timing parameters

? Supporting partial array self-refresh

? Supporting double-bit error detection and single-bit error correction ECC

? Automatic DRAM initialization sequence or by software

? Supporting a maximum of 4 PCI-E3.0 controllers by configuration, with output data rates of 8Gbps, 5Gbps, and 2.5Gbps

? Supporting 2 SATA3.0 controllers by configuration, with output data rates of 6Gbps, 3Gbps, and 1.5Gbps

? Supporting 4 Gigabit Ethernet controllers with SGMII output b configuration, supporting up to 4 SGMII interfaces for Gigabit

? Supporting 1 10 Gigabit Ethernet (based on the 10GBASE-R protocol) after configuration

? Compatible with the version 3.0 of PCI-Express Base Specification, backward compatible with 2.0 and 1.1

? Supporting Root Complex (RC) and Endpoint (EP) configurations

? Each supporting x4, x2, and x1 link widths

? Supporting 32-bit and 64-bit addressing and payload sizes up to 256 bytes

? Supporting PCI-Express messaging and interrupts

? 2 SATA3.0 controllers supporting 1.5Gbps, 3.0 Gbps, and 6Gbps operations

? Supporting high-speed descriptor-based DMA

? Supporting Native Command Queuing (NCQ) commands

? Supporting hot swapping, including asynchronous signal recovery

? Host/Device configurable

? Supporting OTG function

? Supporting 6 CAN2.0B interfaces

? Supporting CAN2.0B technical specifications

? Complied with the version 3.0 of SD Host Controller Standard Specification

? Compatible with the version 4.5 of MMC System Specification

? Compatible with the version 3.01 of SD Memory Card Specification and supporting high-capacity SD memory cards

? Compatible with the version 3.0 of SDIO Card Specification

? Interface includes SPI_MOSI, SPI_MISO, SPI_CLK, and 4 chip selects

? Supporting eSPI hosts

? Arbitration lost interrupt, automatic mode switching, switching from master mode to slave mode

? Four UART controllers (2 UART interfaces on the chip)

? Full-duplex operation

? Software-selectable serial interface data format

? All ports can be configured as open-drain drivers

? All ports can optionally generate interrupts when their states change

? Pin function multiplexing between NAND/NOR and GPCM

? Supporting memory banks with capacities up to 4 GB (for NOR and GPCM)

? LCD Interface

? Two 8-channel DMA engines

? SRAM :512KB

? Power domains: 0.8V, 1.2V, 1.8V, 3.3V

? Packaging: FC-PBGA780(23mm * 23mm)

? Complete development environment

? Rich driver library

? Complete application solutions